6. Sequential Logic & Flipflops

组合逻辑电路

组合逻辑电路(Combinatorial logic)是一种逻辑电路,它的任一时刻的稳态输出,仅仅与该时刻的输入变量的取值有关,而与该时刻以前的输入变量取值无关。

组合逻辑电路由各种逻辑门组成,网络中无记忆器件,也无反馈线

时序逻辑电路

时序逻辑电路的输出结果除了依照目前的输入外也和先前的输入有关系。也就是说,时序逻辑拥有储存器件(内存)来存储信息,而组合逻辑则没有。

时序逻辑电路可分为同步和异步时序电路两类。

同步电路的行为,由离散时刻的输入决定,也就是说有一个时钟信号

而异步电路的行为,在任何时刻都可以有输入影响

触发器是同步时序电路当中最基本的储存器件

锁存器是异步时序电路当中最基本的储存器件

触发器(flip-flop)

从功能上,触发器可分为:

- RS - 置零置一触发器

- JK - 多功能触发器

- D - 延迟触发器

- T - 翻转触发器

一个触发器能存储一位二进制数字信息:0 或 1

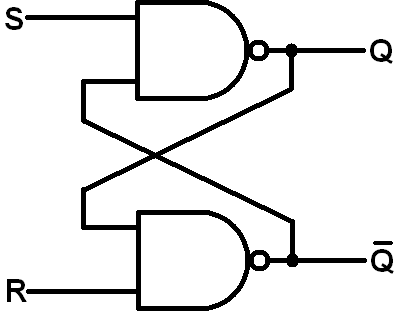

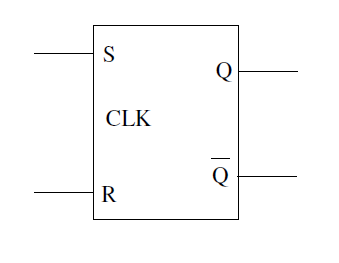

RS 触发器(也称 SR 锁存器)

是触发器中最简单的一种,也是各种其他类型触发器的基本组成部分。

两个 NAND 或 NOR 的输入端输出端进行交叉耦合或首尾相接,即可构成一个基本 RS 触发器。如图

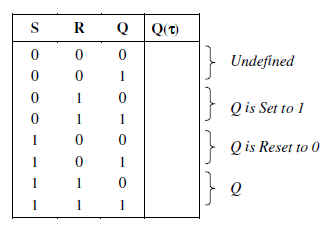

对于 NAND 构成的 RS 触发器,可列出状态表:

进而推导出特征方程:$\large Q_{\text{next}} = S' + RQ$,且需保证 R+S != 0

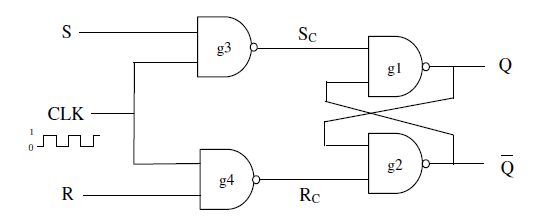

RS 触发器(clocked version)

带有时钟的 RS 触发器(如图),在最前面多了点东西

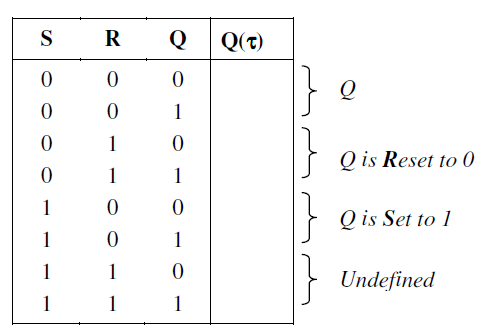

可以推出这种含有时钟的 RS 触发器的状态表是

进而可以发现,S=1, R=0 是 SET;S=0, R=1 是 RESET

当 CLK=0 时,会令 S_C 和 R_C 均为 1,触发器失效;故触发器仅当 CLK=1 生效

这种带有时钟的 RS 触发器,符号为

且含时钟的 RS 触发器,方程为 $\large Q_{\text{next}} = S + R'Q$,且 RS = 0

D 触发器

D 触发器就相当于把含有时钟的 RS 触发器的 S 设置为 R'

当 CLK=1 时,D 触发器的输出与输入相等

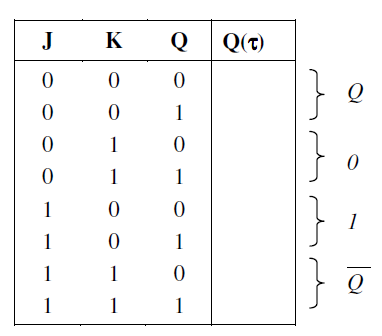

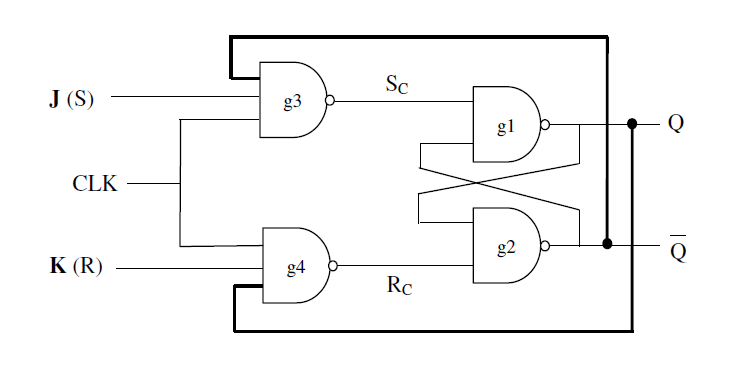

JK 触发器

JK 触发器,是类似于 RS 触发器,只不过允许两个输入同时为 1(此时输出 Q')

方程:$\large Q_{\text{next}} = JQ' + K'Q$,其中 KJ 分别相当于 RS

T 触发器

T 触发器相当于两个输入永远相同的 JK 触发器

方程:$\large Q_{\text{next}} = TQ' + T'Q = T \oplus Q$

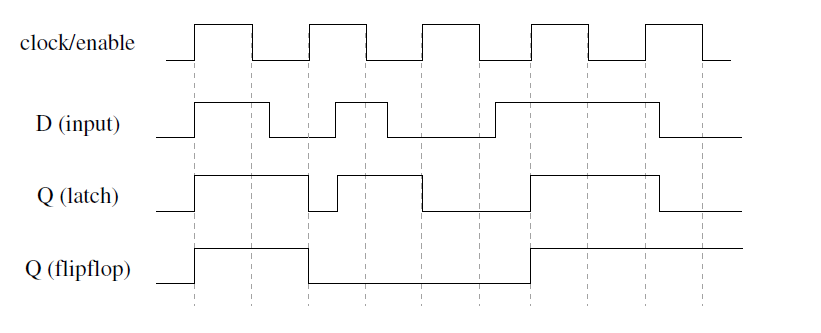

锁存器(latch)

锁存器与触发器很相似,但主要有几点不同:

- 触发器一般会应用于同步电路,而锁存器应用于异步电路

- 锁存器不用时钟来控制信号,而是手动输入的

- 锁存器手动输入的值只要是 1,输出就可以随时随着输入而改变;而触发器只有时钟状态从 0 变为 1 的时候,输出才能改变,如图(以 D 触发器/锁存器为例)

主从触发器(Master-Slave Flip Flop)

由于在普通的锁存器当中,输出值可能会短时间内多次变化。为了解决这个问题,可以使用主从触发器。

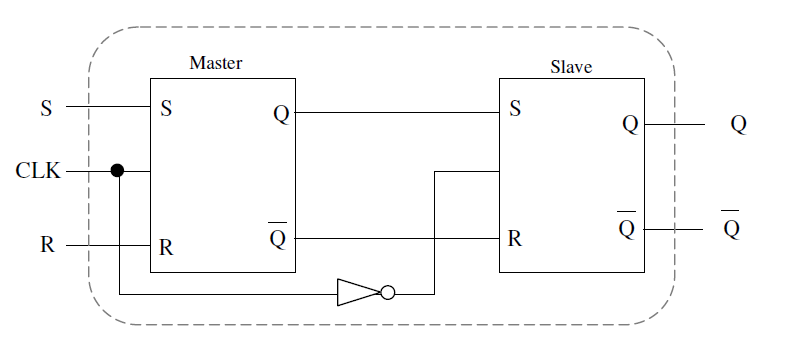

以主从 RS 触发器为例说明,主从 RS 触发器由两个 RS 触发器和一个反相器构成:

可以看到,把反相器接到从触发器和时钟信号中间,就可以让整个主从触发器的输出在一个完整的时钟周期内仅改变一次。

异步输入

触发器通常会包含独立于时钟的输入,从而允许独立于时钟进行设置(PRE)和复位(CLR)操作。这种输入叫做异步输入(Asynchronous Input),用于在正常时钟操作开始之前进行正确的初始化。

触发器的应用

消除接触抖动

接触抖动,例如刚刚按下插排电源的时候,按钮还未固定,可能在开与关的状态之间来回跳。虽然这个反复横跳的时间很短,但是可能会造成不必要的损失。把开关连上一个 RS 触发器就可以消除这个问题。

降频

如利用一个 D 触发器,可将信号频率由 f 降为 f/2。若有多个 D 触发器,能降到 f/2^n

补充

Edge Triggering: In edge triggering the circuit becomes active at negative or positive edge of the clock signal. For example if the circuit is positive edge triggered, it will take input at exactly the time in which the clock signal goes from low to high. Similarly input is taken at exactly the time in which the clock signal goes from high to low in negative edge triggering. But keep in mind after the the input, it can be processed in all the time till the next input is taken.